2013年01月14日11:17 来源:人民网-财经频道

2012年,采用TSV(硅通孔)的三维封装技术继2011年之后再次成为半导体封装业界备受关注的焦点。

1月,JEDEC固态技术协会(JEDEC Solid State Technology Association)发布了以TSV为前提的移动DRAM新标准“JESD229 Wide I/O Single Data Rate”(SDR)。基于TSV的三维封装作为能以低功耗及大带宽连接智能手机及平板电脑用SoC(应用处理器)和DRAM的技术而备受期待。今后,如果供货量很大的便携终端能够采用基于TSV的三维封装技术,就有望加快TSV的低成本化步伐。

三维封装技术是“ICEP-IAAC 2012”的重要议题

在2月举行的“ISSCC 2012”上,美国IBM公司介绍了通过采用基于TSV的三维封装技术,来层叠连接高性能微处理器和缓存的事例。尽管很多情况下都会在微处理器上层叠存储器,但在高性能用途方面,如何为微处理器散热是一大课题。因此,IBM采用了在存储器上层叠微处理器的构造。而且IBM还在开发通过提高层叠芯片之间的密封树脂的导热率,来提高散热性的技术。

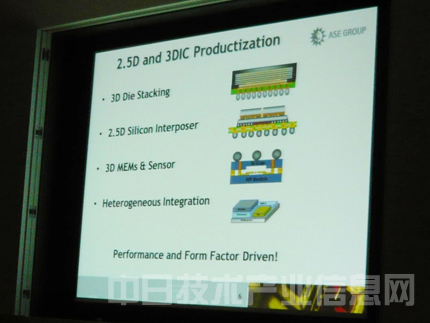

在4月举行的半导体封装技术国际会议“ICEP-IAAC 2012”上,三维封装技术同样成为了一项重要议题。目前,在三维封装技术的业务化方面,最佳供应链模式尚不明确,后工序代工厂商(OSAT)台湾日月光集团提出了多种业务模式,称“大家都在探索最佳解决方法”。

而世界第一大代工企业台积电公司(TSMC)则提出了从晶圆制造到封装组装全部由台积电一家公司负责的总承包模式。通过采用名为“CoWoS(Chip on Wafer on Substrate)”的自主制造技术,可提高组装时的成品率。

不过,这种总承包模式是否会成为今后三维封装技术的主流,目前尚不明确。台积电的竞争对手――美国GLOBALFOUNDRIES公司目前并未大力推介总承包模式,而是十分重视与OSAT等的合作。

关于利用TSV硅转接板的2.5维封装技术,以高端FPGA为主的量产化正在不断推进之中。继28nm工艺之后,20nm以上工艺也与微细化一样被定位于实现大规模化、高集成化的核心技术。

在“摩尔法则”正在接近极限的形势下,估计基于TSV的三维封装技术会对今后推进芯片的高性能化、低功耗化起到更加重要的作用。(日经技术在线! 供稿)