2014年04月15日09:06

【新闻链接】

东芝开发出了令SoC积极进入“深度休眠”模式来降低设备耗电量的技术。将该技术应用于电子纸性显示器的信息终端试制品,使试制品的总体耗电量降到了1/2~1/5。东芝打算进一步研发,将其与该公司的SoC结合起来提供。

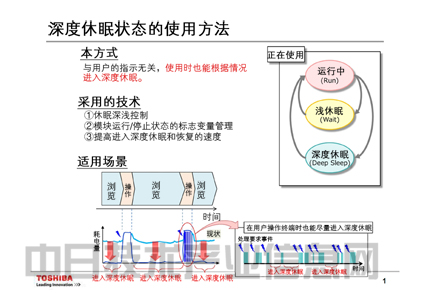

图1 此次开发的省电化技术的概要。即便在用户使用终端时也能寻找时机进入深度休眠状态(图片来源于东芝)

这里所说的深度休眠是指SoC的CPU及外围电路的所有电路块全部停止运行、外部时钟关闭的状态。以前,只有在用户发出挂起(Suspend)指示,或者电池剩余电量低于一定水平时,才会进入深度休眠,而在用户使用中不会进入深度休眠。设备使用中的省电技术,在外部时钟开着的状态下,一直是使用根据情况让CPU及外围电路等电路块停止运行的技术。

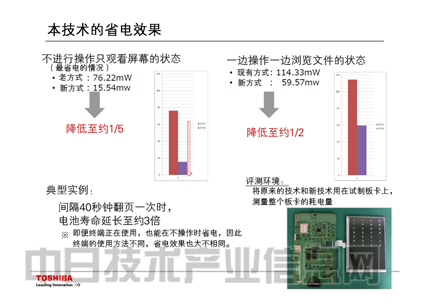

图2 此次技术的省电效果。把该技术应用于连接电子纸型显示器的试制基板评测总体耗电量时得知,最省电的情况下耗电量可降至原来的约1/5(图片来源于东芝)

东芝此次开发的技术,是在终端使用时亦可寻找休息间隙并自动进入深度休眠。是通过开发出了终端是否进入深度休眠的判断技术和将进入深度休眠和恢复的处理高速化技术而实现的。该技术是以改进Linux内核程序的方式安装的。

在装有美国飞思卡尔半导体的SoC“i.MX508”以及电子纸式显示器的评测环境下使用该技术,确认了使用安卓信息终端时的效果。在不操作而只观看屏幕的状态下,以前高达76.22mW的平均耗电量降低到了15.54mW。而且,在操作终端并浏览文件的状态下,平均耗电量由114.33mW降低到了59.57mW。

只要有十数ms以上的闲置时间就能发挥省电作用

进入深入休眠是用以下步骤来判断的。首先,确认外围电路是否在运行。为了能够立即实行判断,导入了用来显示外围电路运行情况的标志变量(Flag)。经过设备驱动程序向外围电路发出处理要求时判断为真,而发生退出处理的中断(Interrupt)时则判断为假。

接下来,如果所有外围电路都停止运行,就会确认距离定时器所设定的下次中断发生还有多长时间。如果该时间长于损益平衡点,就会进入深度休眠。进入深度休眠时,需要将SoC上的最新缓存信息写回DRAM,而恢复时则需要使SoC上的缓存数据无效。由于这些处理需要消耗多余的电力,因此闲置时间不够长,则进入深度休眠就会导致耗电量增加。东芝表示,此次验证的试制品的损益平衡点为13ms左右。

进入深度休眠和恢复速度的提高是用以下两种方法实现的。(1)计时器用硅振荡器代替了水晶振荡器,从而缩短了时钟稳定之前的等待时间;(2)改进了进入深度休眠时将缓存信息写回DRAM,以及恢复时初始化缓存内数据的程序。进入深度休眠的时间由1.1ms缩短到了0.5ms,恢复时间由10ms缩短到了1.8ms。由此,最大限度地抑制了用户操作响应性能的降低。而且,进入深度休眠和恢复时所消耗的电力减少,损益平衡点变小,意味着进入深度休眠更为容易。

另外,该技术不适合用于配备普通液晶显示器的终端。原因是输出影像信号的电路一直处于驱动状态,很难进入深度休眠。该技术适合不使用液晶显示器的M2M(machine to machine,机器对机器)终端,以及配备电子纸等非易失性显示器的终端。

东芝预定在2014年4月14~16日在横滨市举行的“COOL Chips XVII”上就此次的技术发表演讲,题目为“Aggressive Use of Deep Sleep Mode in Low Power Embedded Systems”。(作者:竹居 智久,日经技术在线!供稿)