2014年02月13日08:34

【新聞鏈接】

NEC與日本東北大學的共同研發小組開發出了耗電量可降至原來的1/80的無線傳感器終端用非易失性MCU。技術詳情將在“International Solid-State Circuits Conference(ISSCC)2014”(2014年2月9∼13日,美國舊金山)上發表﹝演講序號:10.5﹞,演講題目為“A 90nm 20MHz Fully Nonvolatile Microcontroller for Standby-Power-Critical Applications”。

左起依次為日本東北大學教授、國際集成電子研發中心長遠藤哲郎﹔日本東北大學教授、節能及自旋電子學集成化系統中心長大野英男﹔NEC綠色平台研究所長中村祐一

試制的300mm晶圓

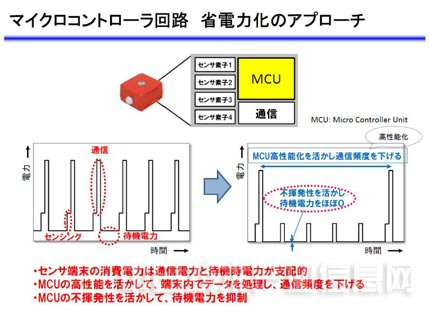

近年來,用於收集大數據的無線傳感器終端的重要性越來越高。無線傳感器終端要求實現小型化和輕量化,可配備的電池容量較小。因此,必須要降低電路的功耗,減少電池的更換頻率。無線傳感器終端通常都是間歇性工作,每隔一定的時間檢測並發送一次信息,電路的運轉率較低。因此,通過使電路實現非易失性,在待機時切斷電源,有望大幅削減耗電量。

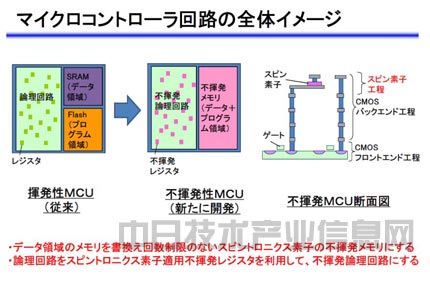

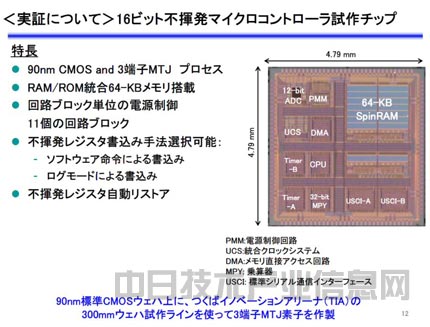

此次試制的16位非易失性MCU在CPU內核、A-D轉換器及乘法器等電路塊上採用由3端子型MTJ元件構成的非易失性寄存器,即使切斷電源也能保持之前的狀態。另外,64KB混載存儲器也採用相同的MTJ元件,使MCU整體實現了非易失性。

削減無線傳感器終端用MCU的待機電力

MCU整體實現非易失性

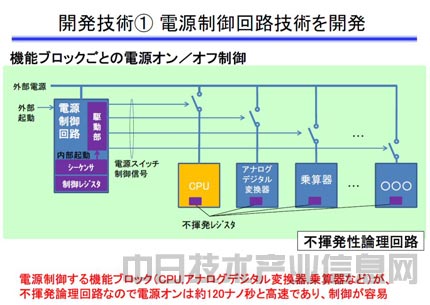

研發小組主要開發了兩種電路技術。一種是控制各電路塊的開/關狀態的電源控制電路。這種電路的主要特點是,把恢復供電所需時間縮短到了約120ns。基於強介電體存儲器(FeRAM)的非易失性MCU的恢復供電所需時間約為400ns。另外,易失性MCU的恢復供電所需時間達到ms級。此次通過在非易失性寄存器上採用可高速、低電壓工作的MTJ元件,成功把邏輯電路和非易失性寄存器的電源統一為1V,簡化了電源控制,由此縮短了恢復供電的時間。

電源控制電路技術

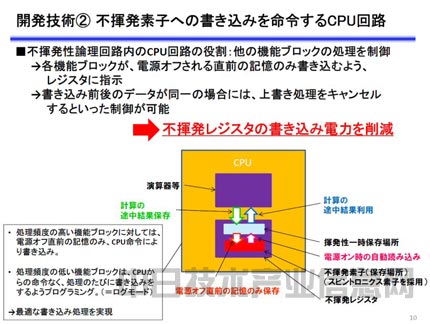

非易失性寄存器的寫入控制電路

另一項技術是控制向非易失性寄存器寫入的電路。該電路可控制各電路塊隻向非易失性寄存器寫入電源切斷前的狀態。另外,寫入前后的數據相同時,通過取消覆蓋處理,把向非易失性寄存器寫入的次數降到了最低。通過這樣的控制,削減了向非易失性寄存器寫入數據所需的電力。

試制的芯片

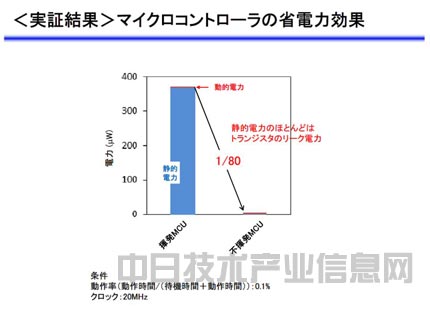

耗電量降至1/80

此次的非易失性MCU在時鐘頻率為20MHz、運轉率為0.1%的條件下工作時,耗電量隻有易失性MCU的1/80。這樣一來,能將無線傳感器終端的電池續航時間延長至原來的約10倍。

試制芯片利用的是90nm工藝CMOS技術和3端子型MTJ工藝。90nm工藝CMOS晶圓由瑞薩電子制造,然后在筑波創新園區的300mm試產線上將MTJ元件嵌入其中。芯片面積為4.79mm見方。芯片的設計組合使用了普通的EDA軟件和自主開發的軟件。另外,此次測試使用的是普通的測試儀,不過,今后實用化時要開發能驗証非易失性的測試技術。計劃2017年前后實現實用化。(作者:木村 雅秀,日經技術在線!供稿)